EUROPEAN AVIATION SAFETY AGENCY AGENCE EUROPÉENNE DE LA SÉCURITÉ AÉRIENNE EUROPÄISCHE AGENTUR FÜR FLUGSICHERHEIT

# Research Project EASA.2011/6 MULCORS - Use of MULticore proCessORs in airborne Systems

easa.europa.eu

#### **Disclaimer**

This study has been carried out for the European Aviation Safety Agency by an external organization and expresses the opinion of the organization undertaking the study. It is provided for information purposes only and the views expressed in the study have not been adopted, endorsed or in any way approved by the European Aviation Safety Agency. Consequently it should not be relied upon as a statement, as any form of warranty, representation, undertaking, contractual, or other commitment binding in law upon the European Aviation Safety Agency.

Ownership of all copyright and other intellectual property rights in this material including any documentation, data and technical information, remains vested to the European Aviation Safety Agency. All logo, copyrights, trademarks, and registered trademarks that may be contained within are the property of their respective owners.

Reproduction of this study, in whole or in part, is permitted under the condition that the full body of this Disclaimer remains clearly and visibly affixed at all times with such reproduced part.

# EASA 2011.C31 "MULCORS" Project.

# The Use of MULticore proCessORS in Airborne Systems"

# **THALES AVIONICS**

# **Dossier ref. CCC/12/006898 – Rev. 07**

Authors : Xavier JEAN, Marc GATTI Guy BERTHON, Marc FUMEY

# REVISIONS

| Revision | Date                            | Effect on § | Description                                     |

|----------|---------------------------------|-------------|-------------------------------------------------|

| 00       | November, 8 <sup>th</sup> 2012  | All         | Draft of the final Report                       |

| 01       | November, 20 <sup>th</sup> 2012 | All         | Creation of the document                        |

| 02       | November, 26 <sup>th</sup> 2012 | All         | Integration EASA remarks, 2012-11-23            |

|          |                                 |             | Complement chapters regarding Tasks 1 & 2       |

| 03       | December, 05 <sup>th</sup> 2012 | 9.3.6.13    | Adding a chapter regarding the Hypervisor       |

| 04       | December, 07 <sup>th</sup> 2012 | 6 & 13      | Upgrade list for Chapters Literature Review and |

|          |                                 |             | References                                      |

| 05       | December, 07 <sup>th</sup> 2012 | None        | Reference number which should the contract      |

|          |                                 |             | number EASA.2011.C31.                           |

|          |                                 |             | Adding ® & ™                                    |

| 06       | December, 08 <sup>th</sup> 2012 | All         | Modification of recommended guidelines          |

|          |                                 |             | following MULCORS final report presentation     |

| 07       | December, 16 <sup>th</sup> 2012 | All         | Modification of recommended guidelines          |

|          |                                 |             | following MULCORS final report presentation     |

|          |                                 |             | comments                                        |

| 1. DISCLAIMER                                                                               | 8        |

|---------------------------------------------------------------------------------------------|----------|

| 2. ACKNOWLEDGEMENTS                                                                         | 9        |

| 3. EXECUTIVE SUMMARY                                                                        | 10       |

| <b>3.1.</b> AIMS / OBJECTIVES                                                               | 10       |

| <b>3.2.</b> OVERALL APPROACH                                                                | 10       |

| <b>3.3. EASA EXPECTATIONS</b>                                                               | 10       |

| <b>3.4.</b> FINDINGS ACHIEVEMENTS AND CONCLUSIONS                                           | 11       |

| 4. BACKGROUND                                                                               | 12       |

| 4.1. DIGITAL EMBEDDED AIRCRAFT SYSTEMS                                                      | 12       |

| 4.2. USE OF COTS PROCESSORS IN EMBEDDED AIRCRAFT EQUIPMENT                                  | 12       |

| 4.3. USE OF MULTI-CORE IN EMBEDDED AIRCRAFT EQUIPMENT                                       | 13       |

| 5. AIMS AND OBJECTIVES                                                                      | 14       |

| 6. LITERATURE REVIEW                                                                        | 15       |

| 6.1. AVIONIC STANDARDS                                                                      | 15       |

| 6.2. OFFICIAL GUIDELINES                                                                    | 16       |

| 6.3. STUDIES ON PROCESSOR EVALUATION AND SELECTION                                          | 16       |

| 6.4. STUDIES ON ROBUST PARTITIONING                                                         | 16       |

| 6.5. STUDIES ON WCET CALCULUS                                                               | 17       |

| 6.6. STUDIES ON MULTICORE PROCESSORS SCHEDULING                                             | 18       |

| 6.7. STUDIES ON HYPERVISORS AND OPERATING SYSTEMS                                           | 18       |

| 6.8. <b>R</b> EFERENCE MANUAL OF STUDIED PROCESSORS                                         | 18       |

| 7. METHODOLOGY                                                                              | 20       |

| 8. IMPLEMENTATION                                                                           | 21       |

| 9. RESULTS AND OUTCOME                                                                      | 23       |

|                                                                                             |          |

| 9.1. REQUIREMENTS FOR AN EMBEDDED AIRCRAFT SYSTEMS                                          | 23       |

| 9.1.1. DETERMINISM IN EMBEDDED AIRCRAFT SYSTEMS                                             | 23       |

| 9.1.1.1. Embedded Aircraft Systems integrity                                                | 23       |

| 9.1.1.2. WCET analyzability                                                                 | 25       |

| 9.1.1.3. Airborne Embedded System Usage Domain                                              | 25       |

| 9.1.1.4. Robust Partitioning                                                                | 26       |

| 9.1.2. CERTIFICATION OBJECTIVES FOR EMBEDDED AIRCRAFT SYSTEMS<br>9.1.2.1. Intended Function | 27<br>28 |

|                                                                                             | 28       |

| 9.1.2.11 BSP or Board Support Package                                          | 29 |

|--------------------------------------------------------------------------------|----|

| 9.1.2.12 Hypervisor                                                            | 29 |

| 9.1.2.13 Operating System                                                      | 30 |

| 9.1.2.14 Device drivers                                                        | 31 |

| 9.1.2.2. Safety Objectives                                                     | 31 |

| 9.1.2.3. Foreseeable Conditions                                                | 32 |

| 9.2. PROCESSORS SELECTION                                                      | 33 |

| 9.2.1. STRATEGIC SELECTION CRITERIA                                            | 33 |

| 9.2.1.1. Selection criteria regarding the manufacturer situation               | 33 |

| 9.2.1.2. Manufacturer openness regarding design and tests information          | 34 |

| 9.2.2. TECHNICAL SELECTION CRITERIA                                            | 34 |

| 9.2.2.1. Focus on core architecture                                            | 34 |

| 9.2.2.11 Instruction model                                                     | 34 |

| 9.2.2.12 Pipeline issues                                                       | 36 |

| 9.2.2.13 Virtual memory management                                             | 37 |

| 9.2.2.14 Private caches and scratchpads                                        | 38 |

| 9.2.2.2. Focus on peripherals                                                  | 39 |

| 9.2.2.3. Focus on hardware assist for debug and monitoring                     | 40 |

| 9.3. MULTI-CORE TECHNOLOGY STATE-OF-THE-ART                                    | 41 |

| 9.3.1. SUMMARY OF TASK 1                                                       | 41 |

| 9.3.2. SUMMARY OF TASK 2                                                       | 41 |

| 9.3.3. Basic Architecture characteristics                                      | 42 |

| 9.3.3.1. Memory sharing architecture                                           | 43 |

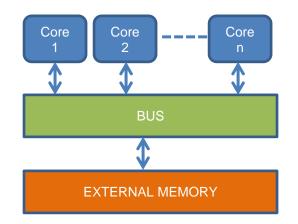

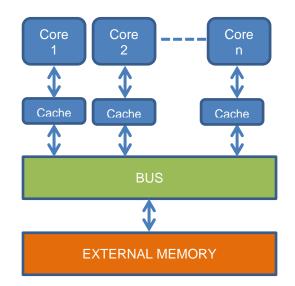

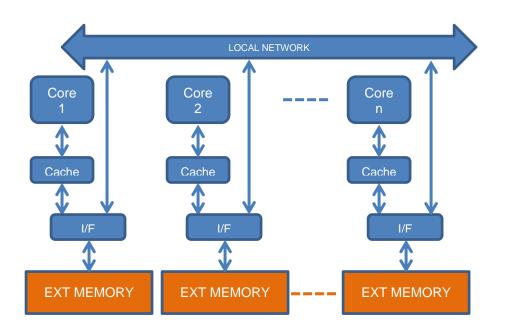

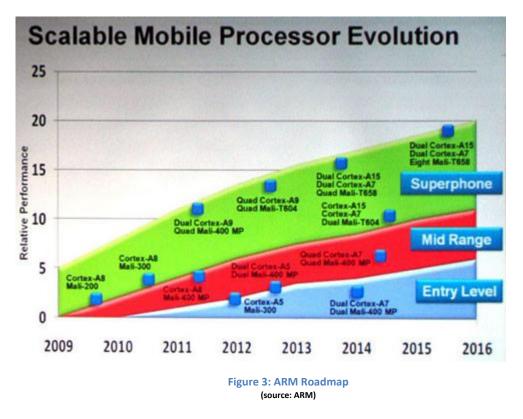

| 9.3.3.11 Unified Memory Access (UMA)                                           | 43 |

| 9.3.3.12 What about caches?                                                    | 44 |

| 9.3.3.13 Distributed Architecture (DA)                                         | 45 |

| 9.3.3.14 Architecture named "Single Address space, Distributed Memory" or SADM | 46 |

| 9.3.4. Multi-core galaxy overview                                              | 47 |

| 9.3.4.1. A short overview of processor roadmap                                 | 47 |

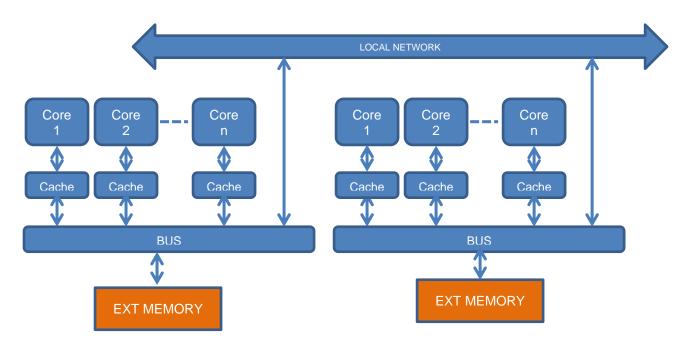

| 9.3.4.11 Freescale Roadmap                                                     | 47 |

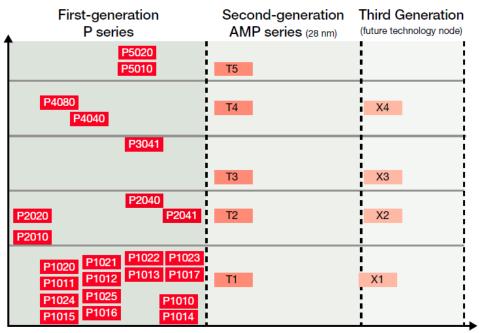

| 9.3.4.12 ARM Roadmap                                                           | 49 |

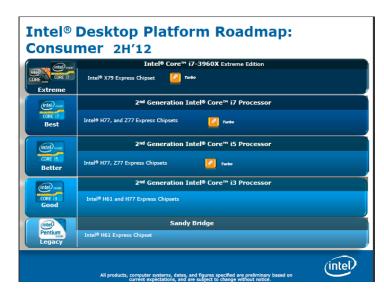

| 9.3.4.13 INTEL <sup>®</sup> ROADMAP                                            | 50 |

| 9.3.4.2. Multi-core processors manufacturers and addressed market segments     | 52 |

| 9.3.4.3. Academic projects around multi-core                                   | 53 |

| 9.3.4.4. Industrial collaborations                                             | 54 |

| 9.3.5. SOFTWARE SUPPORT FOR EMBEDDED AIRCRAFT SYSTEMS                          | 54 |

| 9.3.5.1. Airborne Certified Operating System                                   | 54 |

| 9.3.5.2. Software definition / explanation                                     | 55 |

| 9.3.5.21 Processes and Threads                                                 | 55 |

| 9.3.5.22 Multithreading                                                        | 55 |

| 9.3.5.23 Processes, kernel threads, user threads                               | 55 |

| 9.3.5.3. The impact of multi-cores on Software Development                     | 56 |

| 9.3.5.31 Memory Management                                                     | 56 |

| 9.3.5.32 Mapping                                                               | 57 |

| 9.3.6. EXAMPLES OF REPRESENTATIVE MULTI-CORE ARCHITECTURES                     | 58 |

| 9.3.6.1. Communication and Networking Processor                                | 58 |

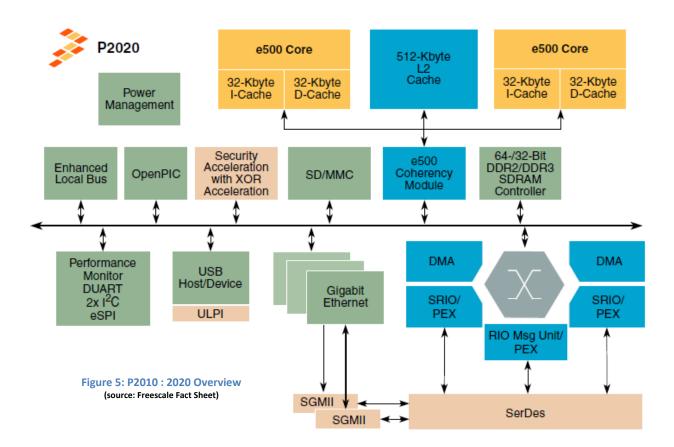

| 9.3.6.11 Freescale QorlQ <sup>™</sup> P2020                                    | 58 |

| 9.3.6.11.1 e500 Coherency Module (ECM) and Address Map                         | 59 |

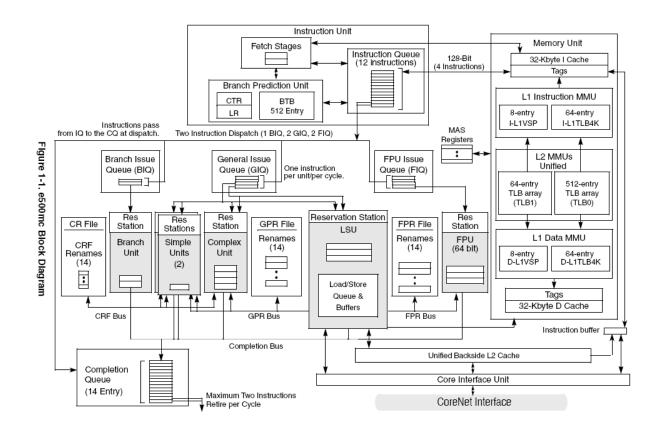

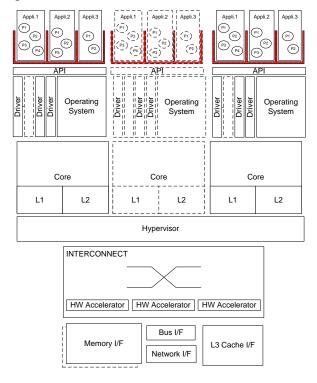

| 9.3.6.12 e500mc Cores                                                          | 60 |

| 9.3.6.13 Hypervisor                                                            | 62 |

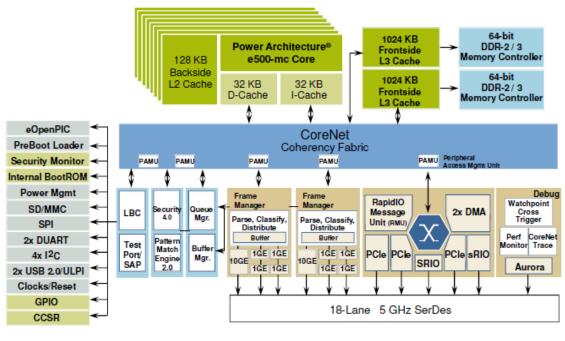

| 9.3.6.14 Networking platform: Freescale QorlQ <sup>™</sup> P4080            | 63  |

|-----------------------------------------------------------------------------|-----|

| 9.3.6.14.1 QorlQ <sup>™</sup> Processor Interconnect                        | 64  |

| 9.3.6.14.2 Peripherals                                                      | 64  |

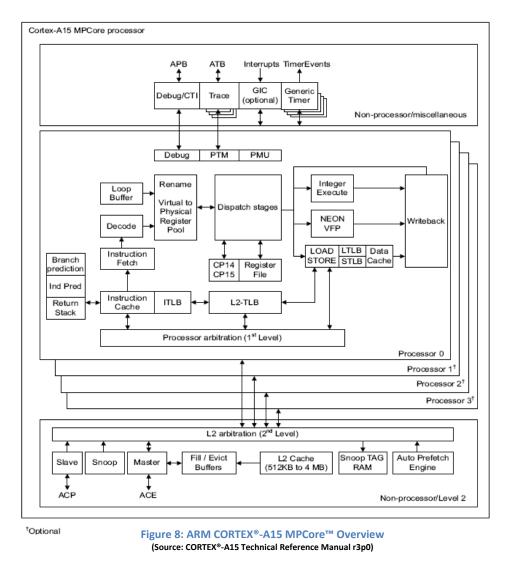

| 9.3.6.2. Low-Power Multi-core IP: ARM CORTEX <sup>®</sup> -A15 MPCore™      | 65  |

| 9.3.6.21 CORTEX <sup>®</sup> -A15 Cores                                     | 66  |

| 9.3.6.22 Snoop Control Unit: First Level interconnect                       | 66  |

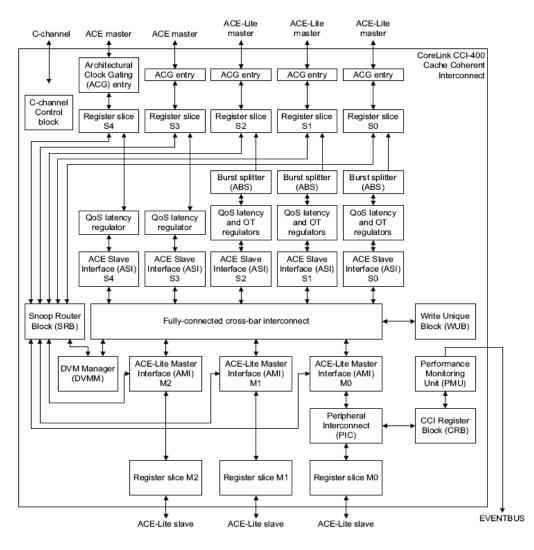

| 9.3.6.23 Corelink <sup>™</sup> Network: Peripheral interconnect             | 67  |

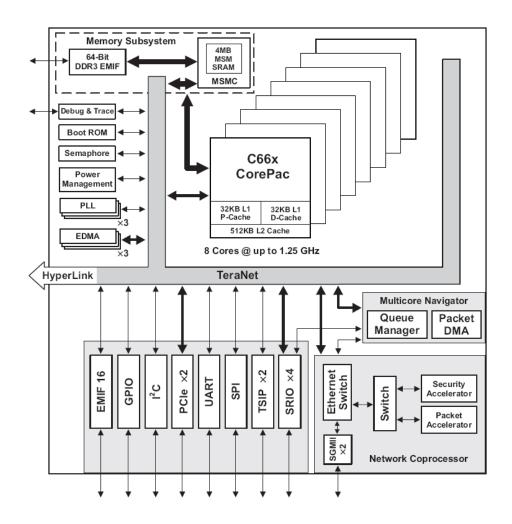

| 9.3.6.3. Multi-core DSP: Texas Instruments TMS320C6678™                     | 68  |

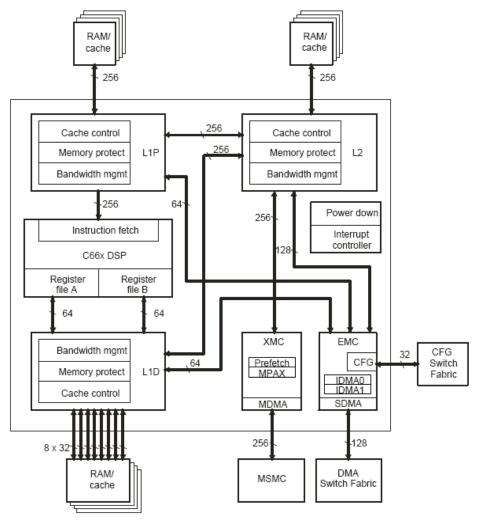

| 9.3.6.31 DSP Cores: C66x <sup>™</sup> CorePac                               | 69  |

| 9.3.6.32 TMS320C66xx <sup>™</sup> interconnect: TeraNet <sup>™</sup>        | 70  |

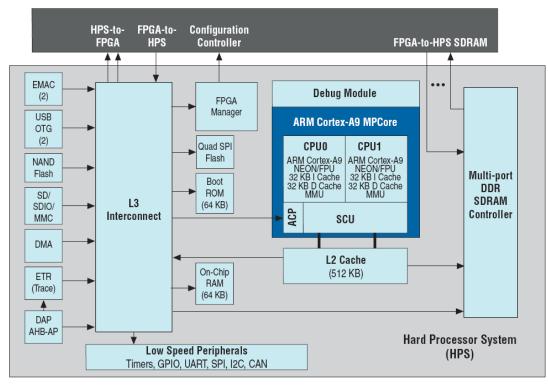

| 9.3.6.4. SoC FPGA Hard Processor System: Altera Cyclone <sup>®</sup> V      | 71  |

| 9.4. MULTI-CORE FEATURES REGARDING CERTIFICATION                            | 72  |

| 9.4.1. INTRODUCTION                                                         | 72  |

| 9.4.2. PROCESSOR FEATURES IMPACT ON DETERMINISM                             | 73  |

| 9.4.2.1. Summary of task 3                                                  | 73  |

| 9.4.2.2. Summary of task 4                                                  | 73  |

| 9.4.2.3. Interconnect                                                       | 73  |

| 9.4.2.31 Overview                                                           | 73  |

| 9.4.2.32 Interconnect Classification criteria                               | 75  |

| 9.4.2.33 Interconnect Usage Domain                                          | 77  |

| 9.4.2.33.1 Objective and Definition                                         | 77  |

| 9.4.2.33.2 Related selection criteria                                       | 79  |

| 9.4.2.34 Interconnect features regarding multi-core processor integrity     | 82  |

| 9.4.2.34.1 Integrity of transactions services in the interconnect           | 82  |

| 9.4.2.34.2 Related selection criteria                                       | 83  |

| 9.4.2.35 Interconnect features regarding Worst Case Execution Time calculus | 83  |

| 9.4.2.35.1 Related selection criteria                                       | 85  |

| 9.4.2.36 Interconnect features regarding Robust Partitioning insurance      | 86  |

| 9.4.2.36.1 Related selection criteria                                       | 86  |

| 9.4.2.4. Shared caches                                                      | 86  |

| 9.4.2.41 Cache Classification criteria                                      | 87  |

| 9.4.2.42 Content prediction features                                        | 88  |

| 9.4.2.43 Classic cache configurations                                       | 89  |

| 9.4.2.43.1 Cache partitioning                                               | 89  |

| 9.4.2.43.2 Cache use as SRAM                                                | 89  |

| 9.4.2.44 Corresponding selection criteria                                   | 90  |

| 9.4.2.5. Cache coherency mechanisms                                         | 91  |

| 9.4.2.51 Corresponding selection criteria                                   | 92  |

| 9.4.2.6. Shared services                                                    | 93  |

| 9.4.2.61 Shared Services Classification criteria                            | 93  |

| 9.4.2.62 Corresponding selection criteria                                   | 96  |

| 9.4.2.7. Cores                                                              | 97  |

| 9.4.2.71 Corresponding selection criteria                                   | 98  |

| 9.4.2.8. Peripherals                                                        | 98  |

| 9.4.2.81 Corresponding selection criteria                                   | 100 |

| 9.5. SOFTWARE ASPECTS                                                       | 101 |

| 9.5.1. SUMMARY OF TASK 7                                                    | 101 |

| 9.5.2. SUMMARY OF TASK 8                                                    | 101 |

| 9.5.3. AIRBORNE SOFTWARE DEPLOYMENT ON A MULTI-CORE PLATFORM                | 101 |

| 9.5.3.1. Airborne Software execution on several cores                       | 101 |

**MULCORS**

| 9.5.3.11 Multitasks scheduling features                                       | 102 |

|-------------------------------------------------------------------------------|-----|

| 9.5.3.12 Airborne Software migration from single-core to multi-core platforms | 103 |

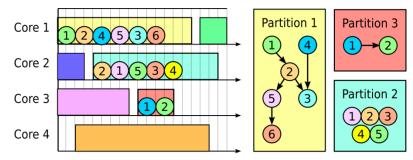

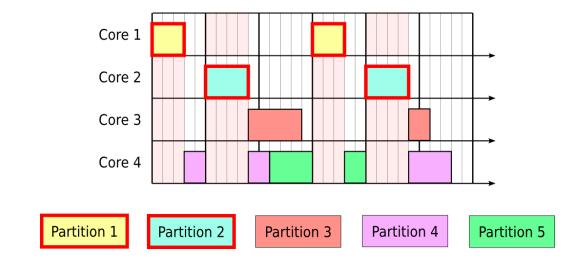

| 9.5.3.13 Partitioned system features                                          | 104 |

| 9.5.3.13.1 Components evolution to take benefit of multi-core platforms       | 104 |

| 9.5.3.13.2 Deployment of partitions                                           | 105 |

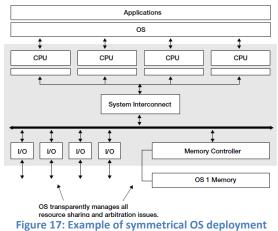

| 9.5.3.13.3 Symmetrical Multi-processing                                       | 105 |

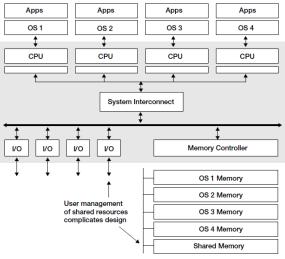

| 9.5.3.13.4 Asymmetrical Multi-processing                                      | 106 |

| 9.5.3.13.5 AMP-SMP-BMP selection                                              | 106 |

| 9.5.3.13.6 Others deployment schemes                                          | 108 |

| 9.5.3.2. Airborne Equipment software features                                 | 109 |

| 9.5.3.21 Architectural concerns                                               | 109 |

| 9.5.3.21.1 Symmetrical Multi Processing                                       | 109 |

| 9.5.3.21.2 Asymmetrical Multi Processing                                      | 110 |

| 9.5.4. MITIGATION MEANS                                                       | 111 |

| 9.5.4.1. Summary of task 5                                                    | 111 |

| 9.5.4.2. Mitigation Means Analysis                                            | 111 |

| 9.5.4.3. Time jitter ratio to total execution time                            | 112 |

| 9.5.4.4. Airborne Software WCET evaluation                                    | 113 |

| 9.5.4.5. Monitoring during real-time execution                                | 113 |

| 9.5.4.6. Airborne Software robustness                                         | 113 |

| 9.6. FAILURE MITIGATION MEANS                                                 | 114 |

| 9.6.1. SUMMARY OF TASK 10                                                     | 114 |

| 9.6.2. MITIGATION MEANS                                                       | 114 |

| 9.7. COTS RELATED FEATURES                                                    | 115 |

| 9.7.1. SUMMARY OF TASK 11                                                     | 115 |

| 9.7.2. COTS RELATED FEATURES ANALYSIS                                         | 115 |

| 9.7.2.1. Electro-migration                                                    | 116 |

| 9.7.2.2. Single Event Effects                                                 | 116 |

| 9.8. METHOD AND TOOLS                                                         | 118 |

| 9.8.1. SUMMARY OF TASK 9                                                      | 118 |

| 9.8.2. METHODS AND TOOLS ANALYSIS                                             | 118 |

| 9.9. EASA GUIDELINE FOR MULTI-CORE PLATFORMS                                  | 121 |

| 9.9.1. SUMMARY OF TASK 6                                                      | 121 |

| 9.9.2. PROPOSED GUIDELINE                                                     | 121 |

|                                                                               | 121 |

|                                                                               | 122 |

| <u>10.</u> OUTREACH                                                           | 123 |

|                                                                               |     |

| <u>11. CONCLUSIONS</u>                                                        | 124 |

|                                                                               |     |

| <b>11.1.</b> CONCLUSIONS WITH RESPECT TO THE REDUCTION OF COMPLEXITY          | 124 |

| <b>11.2.</b> MULTI-CORE PROCESSOR USAGE DOMAIN RELATED CONCLUSIONS            | 125 |

| 11.3. SIGNIFICANT FEATURES RELATED CONCLUSIONS                                | 125 |

| 11.4. CONCLUSIONS ON ROBUST PARTITIONING                                      | 125 |

| <b>11.5.</b> CONCLUSIONS ON SUGGESTED MODIFICATION TO EASA GUIDANCE           | 126 |

| 11.5.1. ROUTES TO COMPLIANCE                                                  | 126 |

| 11.5.2. Advanced guidance                                                     | 126 |

|                                                                               |     |

| 12. RECOMMENDATIONS                                                           | 127 |

| THALES | MULCORS | EASA |

|--------|---------|------|

|--------|---------|------|

| PURPOSE                                                                 | 127                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PROCESSOR SELECTION GUIDE                                               | 129                                                                                                                                                                                                                                                                                                                                                                                                        |

| USAGE DOMAIN                                                            | 132                                                                                                                                                                                                                                                                                                                                                                                                        |

| CACHE COHERENCY                                                         | 133                                                                                                                                                                                                                                                                                                                                                                                                        |

| OPERATING SYSTEM & TASKS ALLOCATIONS                                    | 134                                                                                                                                                                                                                                                                                                                                                                                                        |

| SHARED SERVICES                                                         | 134                                                                                                                                                                                                                                                                                                                                                                                                        |

| CORES                                                                   | 135                                                                                                                                                                                                                                                                                                                                                                                                        |

| PERIPHERALS                                                             | 135                                                                                                                                                                                                                                                                                                                                                                                                        |

| FAILURE MITIGATION                                                      | 135                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                            |

| EFERENCES                                                               | 136                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                            |

| PPENDIXES                                                               | 138                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                            |

| REVIEW OF EXISTING EASA GUIDANCE IN EASA CM SWCEH-001 ISS. 1 REV. 1     | 138                                                                                                                                                                                                                                                                                                                                                                                                        |

| REVIEW OF EASA CM SWCEH-001                                             | 138                                                                                                                                                                                                                                                                                                                                                                                                        |

| MULTI-CORE ASPECTS ALREADY AVAILABLE IN EASA CM SWCEH-001 ISS. 1 REV. 1 | 142                                                                                                                                                                                                                                                                                                                                                                                                        |

| STRUCTURING ACTIVITIES                                                  | 142                                                                                                                                                                                                                                                                                                                                                                                                        |

| EXAMPLE OF PROCESSOR CLASSIFICATION                                     | 145                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                         | PROCESSOR SELECTION GUIDE<br>USAGE DOMAIN<br>CACHE COHERENCY<br>OPERATING SYSTEM & TASKS ALLOCATIONS<br>SHARED SERVICES<br>CORES<br>PERIPHERALS<br>FAILURE MITIGATION<br>EFERENCES<br>PPENDIXES<br>REVIEW OF EXISTING EASA GUIDANCE IN EASA CM SWCEH-001 ISS. 1 REV. 1<br>REVIEW OF EASA CM SWCEH-001<br>MULTI-CORE ASPECTS ALREADY AVAILABLE IN EASA CM SWCEH-001 ISS. 1 REV. 1<br>STRUCTURING ACTIVITIES |

#### **1. DISCLAIMER**

This study has been carried out for the European Aviation Safety Agency by an external organization and expresses the opinion of the organization undertaking the study. It is provided for information purposes only and the views expressed in the study have not been adopted, endorsed or in any way approved by the European Aviation Safety Agency. Consequently it should not be relied upon as a statement, as any form of warranty, representation, undertaking, contractual, or other commitment binding in law upon the European Aviation Safety Agency.

Ownership of all copyright and other intellectual property rights in this material including any documentation, data and technical information, remains vested to the European Aviation Safety Agency. None of the materials provided may be used, reproduced or transmitted, in any form or by any means, electronic or mechanical, including recording or the use of any information storage and retrieval system, without express written consent from the European Aviation Safety Agency. All logo, copyrights, trademarks, and registered trademarks that may be contained within are the property of their respective owners.

Persons wishing to reproduce in whole or in part the contents of this study are invited to submit a written request to the following address:

European Aviation Safety Agency (EASA) Safety Analysis and Research Department Research Project Manager Ottoplatz 1 D-50679 Cologne Germany

#### 2. ACKNOWLEDGEMENTS

This report concludes the MULCORS project contracted with EASA. It provides the main outputs, recommendations and conclusions per EASA Specifications attached to the Invitation to Tender EASA.2011.OP.30.

Project MULCORS - The Use of MULticore proCessORS in Airborne Systems was organized into a set of tasks conducted with reference to the required subject and scope of the contract.

Interim reports were produced at dedicated milestones along with the execution of tasks whose results are further described in the Results and Outcome section 8 of the present report.

Thales would like to thank EASA, both for funding this study project and for its contribution in the reviews of the tasks performed, and its feedback on interim provided reports.

Thales acknowledges the contribution of Xavier Jean, PHD engineer that provided a high level of expertise in the technical matters that were necessary to support such a study.

Finally, the authors of this report recognize the quality of the input from all skilled technical experts and experienced key personnel that were allocated to the project.

#### 3. EXECUTIVE SUMMARY

This section summarizes the overall content of this report as a result of MULCORS study.

#### 3.1. AIMS / OBJECTIVES

MULCORS aims and objectives are

- To provide a survey of Multi-core processors market availability

- To define multi-core processors assessment & selection criteria

- To perform investigations on a representative multi-core processor

- To identify mitigation means, design and usage rules & limitations

- To suggest recommendations for multi-core processor introduction

- And to suggest complementary or modification to EASA guidance

#### **3.2. OVERALL APPROACH**

To cover this study, EASA and Thales have decided to cut it in 12 steps. Each step paves the road to analyze how to introduce safely Multi-Core processor in Embedded Aircraft Systems point per point.

The approach taken in conducting this study was a "Top-Down" one, which consisted in starting with a survey and analysis of the main specific features of a selection of COTS Multi-core Processors, then in establishing recommendations that can be used by EASA to complement its guidance, and by applicants in the determination of compliance of COTS Multi-core Processors with certification requirements.

This approach may be compared to another approach, i.e. more bottom-up, that would be more suited for a developer of a computing unit implementing COTS Multi-core processors. In that context, such an approach should start with the establishment of requirements specifications for the Airborne Electronic Hardware (AEH), taking into account design requirements in relationship with the use of a selected COTS Multi-core processor.

This approach helps to analyze all the stakes for Multi-core Processor introduction in Embedded Aircraft Systems from Market evolution regarding Hardware and Software up to mitigation to be implemented for Risk Management.

#### **3.3. EASA EXPECTATIONS**

The objective of the study was to provide EASA with sufficient data, analyses and recommendations to enable EASA to have a better understanding of the state of the art concepts/features related to  $MCP^1$  and their subsequent impact on the compliance demonstration to finally write and publish guidance material on the subject of the use of multi-core processors in safety-critical airborne systems.

<sup>&</sup>lt;sup>1</sup> MCP : Muti-Core Processor

# 3.4. FINDINGS ACHIEVEMENTS AND CONCLUSIONS

This report contains one section dedicated for recommendations to help building a guideline for COTS multi-core processor introduction.

From Thales point of View introduction of processor multi-core in Embedded Aircraft Systems can be considered as inevitable due to the market evolution where single core processors aims to disappear.

Avionics needs to master multi-core processor introduction in certified Embedded Aircraft Systems such as Displays, IMA systems, Flight Control System, Breaking-Steering System, FADEC, Avionics Server, etc.

To reach this goal, Thales Avionics position is to propose recommendations to complement current EASA guideline (ED80 / EASA Cert. Memo SWCEH-001 issue: 01, Rev. 1) on (Highly) Complex COTS with the following additional recommendations for component selection and implementation:

- Interconnect analysis allowing defining its Domain Usage.

- Interconnect Usage Domain definition:

- $\circ$  This includes the Methodology to ensure the completeness and validation of the Usage Domain which guarantees the compatibility with current Avionics constraints associated to the envisioned usage (DAL<sup>2</sup>) whatever the Airborne System type.

- This is the key point where Airborne System Provider, Certification Applicant and Certification Authorities have to agree on COTS for acceptability.

- Mechanisms to manage Interconnect Usage Domain.

- Operating System or Scheduler:

- Tasks or Processes allocation

- Needs for Hypervisor

- Cache management.

- Core management.

- Shared services at COTS device level.

<sup>&</sup>lt;sup>2</sup> DAL : Design Assurance Level

#### 4. BACKGROUND

# 4.1. DIGITAL EMBEDDED AIRCRAFT SYSTEMS

Embedded Aircraft Systems are composed of Airborne Software installed on Hardware elements. That Airborne Software must fulfill the requirements for safety critical functionality on the aircraft.

Thus, the design, development, certification and operation of the software have to meet Reliability, Availability, Maintainability and Safety (RAMS) objectives depending on their Design Assurance Level (DAL).

Hardware (HW) and Software (SW) components have followed the evolution of technology over the last decades, including technological transitions. Yet the confidence in RAMS of the overall system has not been degraded. Similarly, an equivalent level of safety is expected by Thales from the use of COTS multi-core technology.

#### 4.2. USE OF COTS PROCESSORS IN EMBEDDED AIRCRAFT EQUIPMENT

One major technological step in the Embedded Aircraft Equipment was the introduction of Commercial Off The Shelf (COTS) processors in avionics.

COTS processor architectures have become more and more complex from single CORE requiring external bridge to interconnect Busses and memories (like in the PPC G3 type) up to Micro-Controllers where a bridge has been embedded in the processor (like in the PPC G4 type) with other features such as network (Ethernet), video, audio, bus (USB, PCI, PCIe, etc.) and other interfaces.

Use of COTS multi-core processors technology in safety-critical Airborne Software tends to be the preferred and undisputed choice for the future generation of Airborne Embedded Systems to satisfy processing performance requirements and weight reduction of digital electronic hardware in avionics.

Those COTS multi-core processors are classified like the current micro-controller ones as Highly Complex COTS as they feature quite a number of highly integrated execution units and associated control mechanisms embedded in the device.

In addition, internal architecture may not be directly accessible to the developers implementing such devices in their design.

COTS Multi-core design data, understood as either ED-80/DO-254-usable life-cycle data, or component's in-house development data, is generally not available for review and remains proprietary to the component manufacturer. Hence difficulties arise when design assurance must be shown and demonstrated.

# 4.3. USE OF MULTI-CORE IN EMBEDDED AIRCRAFT EQUIPMENT

The introduction of COTS multi-core processors in Embedded Aircraft Equipment is motivated by the following aspects:

- Provide a long-term answer to the increasing demand of processing power for the embedded hardware elements with an acceptable power consumption and weight (reduce environmental footprint comparing to the current ones).

- Anticipate the mass market obsolescence for single-core processors.

- A first step can be to be able to solve single core obsolescence by the replacement of this single-core by a multi-core with only one active core, others are disabled.

- Expected from COTS Multi-core use in Embedded Aircraft Equipment is a combination of three factors :

- Increased performance,

- There is law for predicting the performance ratio regarding the numbers of cores (Amdhal Law, Gustafson Law) and the number of Threads that can be executed in parallel

- Increased integration

- Less equipment to realize the same functionality or the same amount of equipment to host more functionality.

- Reduce environmental footprint

- Fewer embedded equipment, less power consumption, less dissipation compared to the single core equivalent.

- Be able to "simplify" the use of a Multi-Core Processor thanks to its throughput.

- With, for example, a partitioned architecture, implementing a high DAL level Airborne Software application on one core exchanging data with a low level Airborne Software application implemented on an another core. Arbitration can be made to favor the High DAL level Airborne Software application offering safety for this level.

#### 5. AIMS AND OBJECTIVES

The basis for the project was to conduct a study of the multi-core processors that are currently available and that are anticipated within the next few years, based on public information and roadmap.

The objective of the study was to provide EASA with sufficient data, analyses and recommendations to enable EASA to write and publish guidance material on the subject of the use of multi-core processors in safety-critical airborne systems.

The study examined different Hardware (HW) and Software (SW) architectures of multi-core processors to determine which characteristics of these architectures would enable them to host safety-critical Airborne Software and which have negative implications in terms of the ability of the systems to host safe, robustly partitioned and deterministically executed Airborne Software.

We have then reduced the scope to a selection of few candidates representative of various implementations, which were examined in detail in the study so as to highlight the significant characteristics of the group that are new or different from those of single core processors, whether the characteristics are favorable or unfavorable for the use of the type in safety-critical Airborne Software, and whether any mitigation measures might be used in each case to adapt the type for use in safety-critical Airborne Software.

One purpose of MULCORS was to introduce criteria for multi-core architectures in order to ease their evaluation by the certification authorities in a certification process.

We further distinguished two classes of evaluation criteria:

- Multi-core specific criteria that would be irrelevant in a non-multi-core context

- Complex COTS criteria that are relevant both for multi-core and non-multi-core computing platforms.

Another objective of MULCORS was to use the EASA "Certification Memorandum for Complex Electronic Hardware (CEH)" recommendations in regard to the multi-core technology. This analysis should result in a proposition regarding specific recommendations linked to the multi-core context.

The study examined other aspects such as:

- Software aspects of using multi-core processors to host safety-critical Airborne Software, including any Supervisor / Hypervisor and Operating System.

- Tools and techniques that may be used to specify the software requirements and the software design so as to efficiently and safely execute software in parallel on multi-core processors.

- Verification and certification implications of hosting software on multi-core processors, including measuring the Worst Case Execution Time.

# 6. LITERATURE REVIEW

# 6.1. AVIONIC STANDARDS

SAE ARP 4754: Certification Considerations for Highly-Integrated or Complex Aircraft Systems Society of Automotive Engineers (SAE), 1996.

This standard addresses problematic that deal with complex embedded systems included but not

This standard addresses problematic that deal with complex embedded systems, included but not restricted to digital avionics systems

- *RTCA DO-178B*: Software Considerations in Airborne Systems and Equipment Certification.

*Radio Technical Commission for Aeronautics (RTCA), 1992.* This standard deals with quality of software conception, development, test and integration.

- *RTCA DO-178C*: Software Considerations in Airborne Systems and Equipment Certification.

*Radio Technical Commission for Aeronautics (RTCA), 2012.* This standard is an update of DO-178B

- *RTCA DO-254 / EUROCAE ED-80:* Design Assurance Guidance for Airborne Electronic Hardware. *Radio Technical Commission for Aeronautics (RTCA)* and *EURopean Organisation for Civil Aviation Equipment (EUROCAE)*.

This standard deals with design quality for hardware elements.

• *RTCA DO-297*: Integrated Modular Avionics (IMA) Development, Guidance and Certification Considerations.

# Radio Technical Commission for Aeronautics (RTCA), 2005.

This is the latest standard for IMA systems development and exploitation. It deals with high-level requirements, Robust Partitioning, Verification and Validation, reuse of components.

• *EASA CM - SWCEH – 001, issue 1:* Development Assurance of Airborne Electronic Hardware, August 2011

This certification memorandum has been developed by EASA to highlight issues that shall be addressed in the certification process.

http://www.easa.europa.eu/certification/docs/certification-memorandum/EASA%20CM-SWCEH-001%20Development%20Assurance%20of%20Airborne%20Electronic%20Hardware.pdf

EASA CS-25: Certification Specifications and Acceptable Means of Compliance for Large Aeroplanes, Amendment 12 – subpart F, July 2012 <u>http://www.easa.europa.eu/agency-measures/docs/certification-specifications/CS-25/CS-25%20Amdt%2012.pdf</u>

# 6.2. OFFICIAL GUIDELINES

ARINC-653 P1 revision 3: Avionics Application Software Standard Interface.

Aeronautical Radio Inc, 2010.

This guideline deals with partitions definition and scheduling, Operating System architecture and the Application Executive interface (APEX) that is a standardized API for the embedded partitions.

ARINC-651: Design Guidance for Integrated Modular Avionics. Aeronautical Radio Inc, 1991. This guideline addresses software and hardware concerns in the previous generation of IMA.

#### 6.3. STUDIES ON PROCESSOR EVALUATION AND SELECTION

- Forsberg, H. & Karlsson, K. COTS CPU Selection Guidelines for Safety-Critical Applications 25th Digital Avionics Systems Conference, IEEE/AIAA, 2006, 1-12 <u>http://dx.doi.org/10.1109/DASC.2006.313701</u>

- Bob, G.; Joseph, M.; Brian, P.; Kirk, L.; Spencer, R.; Nikhil, G.; Daniel, O.; Jason, D. L.; John, S.; Arnold, N.; Bob, M. & Dr. Rabi, M.

*Handbook For The Selection And Evaluation Of Microprocessors For Airborne Systems* Federal Aviation Administration - U.S. Department of Transportation, 2011 http://www.faa.gov/aircraft/air\_cert/design\_approvals/air\_software/media/AR\_11\_2.pdf

- Faubladier, F. & Rambaud, D. Soc Survey Report Safety Implications of the use of system-on-chip (SoC) on commercial of-the-shelf (COTS) devices in airborne critical applications EASA – study ref. EASA.2008.OP.04, 2008

<u>http://www.easa.europa.eu/safety-and-research/research-projects/docs/large-aeroplanes/Final\_Report\_EASA.2008\_1.pdf</u>

- Kinnan, L.M. Use of multi-core processors in avionics systems and its potential impact on implementation and certification.

28th Digital Avionics Systems Conference, IEEE/AIAA, 2009, pp. 1.E.4.1 1.E.4-6 http://dx.doi.org/10.1109/DASC.2009.5347560

# 6.4. STUDIES ON ROBUST PARTITIONING

• Rushby John, *Partitioning in Avionics Architectures: Requirements, Mechanisms, and Assurance.* 1999

FAA-AR-99/58, Office of Aviation Research, Washington DC <u>http://www.tc.faa.gov/its/worldpac/techrpt/ar99-58.pdf</u>

- Wilding Matthew M., David S. Hardin, David A. Greve, *Invariant Performance: A statement of Task Isolation Useful for Embedded Application Integration. 1999* Proceedings of the conference on Dependable Computing for Critical Applications <u>http://dl.acm.org/citation.cfm?id=555298.789914</u>

- Littlefield-Lawwill, J. & Kinnan, L., System considerations for robust time and space partitioning in Integrated Modular Avionics. 2008 27th Digital Avionics Systems Conference, IEEE/AIAA, 2008 <u>http://dx.doi.org/10.1109/DASC.2008.4702751</u>

# 6.5. STUDIES ON WCET CALCULUS

- Wilhelm, R.; Engblom, J.; Ermedahl, A.; Holsti, N.; Thesing, S.; Whalley, D.; Bernat, G.; Ferdinand, C.; Heckmann, R.; Mitra, T.; Mueller, F.; Puaut, I.; Puschner, P.; Staschulat, J. & Stenström, P. *The worst-case execution-time problem overview of methods and survey of tools*, *2008 ACM Trans. Embed. Comput. Syst.*, *ACM*, **2008**, *7*, 36:1-36:53 <u>http://www.cs.fsu.edu/~whalley/papers/tecs07.pdf</u>

- Hardy, D. Analyse pire cas pour processeur multi-cœurs disposant de caches partagés (link in French), 2010

PhD Thesis, Université Rennes 1

http://tel.archives-ouvertes.fr/docs/00/55/70/58/PDF/Hardy20101209\_phd.pdf

- Nowotsch, J. & Paulitsch, M., *Leveraging Multi-core Computing Architectures in Avionics*, 2012 European Dependable Computing Conference, IEEE Computer Society, 2012, 0, 132-143 <u>http://doi.ieeecomputersociety.org/10.1109/EDCC.2012.27</u>

- Pellizzoni, R. & Caccamo, M. Impact of Peripheral-Processor Interference on WCET Analysis of Real-Time Embedded Systems, 2010 IEEE Trans. Comput., IEEE Computer Society, 2010, 59, 400-415 http://dx.doi.org/10.1109/TC.2009.156

- Moscibroda, T. & Mutlu, O. Memory performance attacks: denial of memory service in multi-core systems, 2007

Proceedings of 16th USENIX Security Symposium on USENIX Security Symposium, USENIX Association, 2007, 18:1-18:18

<a href="http://dl.acm.org/citation.cfm?id=1362903.1362921">http://dl.acm.org/citation.cfm?id=1362903.1362921</a>

# 6.6. STUDIES ON MULTICORE PROCESSORS SCHEDULING

Davis, R. & Burns, A. A Survey of Hard Real-Time Scheduling Algorithms and Schedulability Analysis Techniques for Multiprocessor Systems, 2009 ACM Comput. Surv., ACM, 2011, 43, 35:1-35:44 http://doi.acm.org/10.1145/1978802.1978814

# 6.7. STUDIES ON HYPERVISORS AND OPERATING SYSTEMS

- Krodel, J. & Romanski, G. Handbook for Real-Time Operating Systems Integration and Component Integration Considerations in Integrated Modular Avionics Systems, 2008 Federal Aviation Administration - U.S. Department of Transportation, 2008 http://www.tc.faa.gov/its/worldpac/techrpt/ar0748.pdf

- Gu, Z. & Zhao, Q. A State-of-the-Art Survey on Real-Time Issues in Embedded Systems Virtualization, 2012 Journal of Software Engineering and Applications, 2012, 05, 277 – 291 http://dx.doi.org/10.4236/jsea.2012.54033

# 6.8. REFERENCE MANUAL OF STUDIED PROCESSORS

- Freescale Embedded Hypervisor Software User Manual http://www.freescale.com/infocenter/index.jsp?topic=%2FQORIQSDK%2F1331445.html

- Freescale Semiconductor Inc, *P4080 QorIQ Integrated Multicore Communication Processor Family Reference Manual*, *01/2012* - Revision. 1 <u>http://www.freescale.com/webapp/sps/site/prod\_summary.jsp?code=P4080</u> (a free account must be created to download the reference manual)

- Freescale Semiconductor Inc, EREF 2.0: A Programmer's Reference Manual for Freescale Power Architecture® Processors, 09/2011 – Revision 0 http://cache.freescale.com/files/32bit/doc/ref\_manual/EREF\_RM.pdf

- Freescale Semiconductor Inc, *e500mc Core Reference Manual*, *03/2012* Revision 1 http://cache.freescale.com/files/32bit/doc/ref\_manual/E500MCRM.pdf

- ARM, *Cortex*<sup>TM</sup>-*A15 MPCore*<sup>TM</sup> *Technical Reference Manual Revision: r3p2, 07/2012* http://infocenter.arm.com/help/topic/com.arm.doc.ddi0438g/DDI0438G\_cortex\_a15\_r3p2\_trm.pdf

- ARM, *CoreLink<sup>TM</sup> CCI-400 Cache Coherent Interconnect Technical Reference Manual*, *11/2012* http://infocenter.arm.com/help/topic/com.arm.doc.ddi0470g/DDI0470G\_cci400\_r1p1\_trm.pdf

- ARM, *ARM Architecture Reference Manual ARMv7-A and ARMv7-R edition, 2012* <u>http://infocenter.arm.com/help/index.jsp?topic=/com.arm.doc.subset.architecture.reference/index.html</u> (an account must be created to access this document)

- Texas Instruments, *TMS320C6678<sup>™</sup> Multicore Fixed and Floating-Point Digital Signal Processor*, 02/2012 http://www.ti.com/lit/ds/sprs691c.pdf

• Texas Instruments, *TMS320C66x<sup>™</sup> DSP CorePac User Guide*, 07/2011 http://www.ti.com/lit/ug/sprugw0b/sprugw0b.pdf

# 7. METHODOLOGY

Besides the organization in tasks described in section 8 below, this study was organized as follows:

- 1. A preliminary phase which was divided in two part

- The first part where we have defined some requirements applicable to multi-core computing platforms in an avionic context. Those requirements depend on the different kinds of digital systems and their level of criticality.

- The second part that deals with processors selection for avionic usage out of the field of multicore architecture. Two kinds of selection criteria were explored: strategic criteria that deal with manufacturer selection rather than the processor itself, and technical criteria that focus on specific points of the architecture. Those criteria are still valid in a multicore context.

- 2. A first phase was prospective: we provided a snapshot of the multi-core technology and basic nontechnical criteria for processors early selection. Then we presented some representative multi-core computing platforms in a more detailed description.

- 3. A second phase of the study refined multi-core features on the hardware and software aspects. We illustrate those features on two selected computing platforms. We provided a set of guidelines and technical selection criteria.

- 4. A third phase where we deduced from the previous phases additional recommendations for certification procedures.

#### 8. IMPLEMENTATION

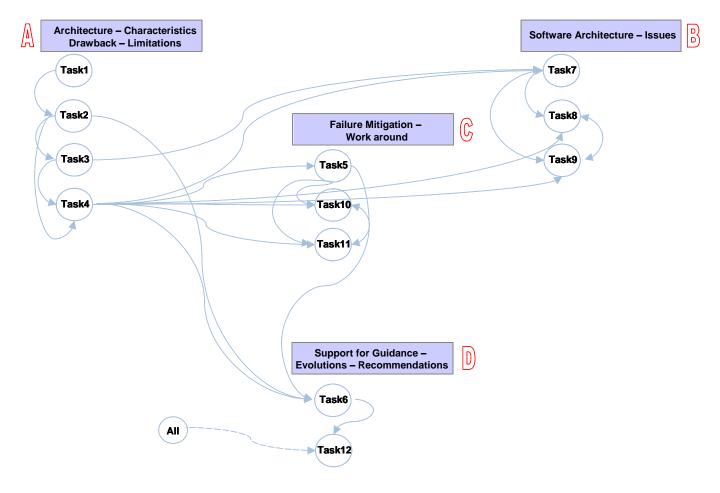

The work relevant for this study has been implemented, based on different activities organized in tasks, and deployed in a logical manner. A summary of those tasks and their arrangement is provided below to allow a better and easier reference of the results and outcomes exposed in section 8 of this present report.

- **Task 1**. Provide a survey of Multi-core processors market availability

- Task 2. Characterize essential multi-core processors types features

- Task 3. Define multi-core processors assessment & selection criteria

- Task 4. Perform investigations on a representative multi-core processor

- Task 5. Identify mitigation means, design and usage rules & limitations

- Task 6. Suggest complementary or modification to EASA guidance

- Task 7. Investigate operating system software execution related aspects

- Task 8. Identify methods, tools, languages and Operating Systems for design

- **Task 9**. Identify methods, tools, means and instrumentation for testing

- Task 10. Examine failure detection and recovery mechanisms features

- Task 11. Analyze COTS-related features (Errata sheets, SEU, Service experience)

- Task 12. Summary conclusion, main results & recommendations and final report

The task flow execution followed the logic in Figure 1 above with the exception of task 7 that needed to be anticipated earlier than scheduled in the original plan.

A lesson learned from such an organization for a similar project is to limit the breakdown into tasks to less than a few (around 6 tasks) in order to avoid dispersion of issues over too many packages.

Monthly progress reports were provided and presented to EASA. This led to few amendments to the original content both programmatic and technical. Also worth to mention is that interim reports were provided and amended along with each monthly progress reports. This was useful to help reorient the research to actual EASA needs and directions.

A task summary is provided for reference along with the details discussion in the Results and Outcome section 8.

Figure 1: Task Work Flow

# 9. RESULTS AND OUTCOME

# 9.1. REQUIREMENTS FOR AN EMBEDDED AIRCRAFT SYSTEMS

#### 9.1.1. Determinism in Embedded Aircraft Systems

Determinism is an abstract notion that usually references several high level requirements; part of it is described in the DO-297 as "The ability to produce a predictable outcome generally based on the preceding operations, the outcome occurs in a specified period of time with some degree of repeatability".

Depending on the context, its embodiment may vary. Yet in a general case, we can say that a system is deterministic as soon as its behavior is ruled by a set of identified laws. Those laws have to be compatible with certification objectives.

For instance, a device whose response time follows a *Gaussian* law where means and variance are defined may not comply with the usual requirements, such as a finite response time.

In this report, we state that an Embedded Aircraft System is deterministic if it fulfills the following definitions for "*Embedded Aircraft System Determinism*":

- It is possible to ensure the *Execution Integrity* of its Airborne Software. That means correct Airborne Software will be correctly executed in a nominal situation, and the Embedded Aircraft System state will be predictable in non-nominal situations (internal faults). It does not cover the case of faulty airborne software.

- It is possible to perform a *WCET analysis* (Worst Case Execution Time) of the embedded software (Airborne Software and Embedded Aircraft System software). Timing information on the Embedded Aircraft System behavior (e.g. memory access worst case response time) may be necessary.

- When the Embedded Aircraft System provider has no visibility into, or limited constraints enforced towards the embedded Airborne Software(s), he shall define a *Platform Usage Domain* that details restrictions on the Airborne Software development.

- When the Embedded Aircraft System is destined to host a partitioned system, such as in IMA<sup>3</sup>, the Embedded Aircraft System provider shall also ensure *Robust Partitioning* between the hosted partitions.

# 9.1.1.1. Embedded Aircraft Systems integrity

To ensure the execution integrity of embedded software, the Embedded Aircraft System provider must demonstrate that the Embedded Aircraft System mode during non-faulty software execution remains nominal or degraded into an *acceptable* state.

<sup>&</sup>lt;sup>3</sup> IMA : Integrated Modular Avionic

To obtain this guarantee with an adequate level of confidence (according to the Design Assurance Level), the Embedded Aircraft System provider must accumulate sufficient **knowledge** on the processor's internal mechanisms.

Such knowledge can be obtained through datasheets, reference manuals, under dedicated NDA<sup>4</sup>, Communications, White Papers, Application notes, Errata sheets, laboratory test campaigns, etc.

The growing complexity of COTS processor architecture makes a fine grain description of all internal features not accessible for Human, Technical and  $IP^5$  reasons.

Thus the properties of some features can be partially masked as long as the COTS processor manufacturer is able to provide guarantees on their observable behavior.

The main difficulties in ensuring Embedded Aircraft System integrity deal with the determination of its behavior upon the occurrence of internal faults and failures. Therefore, depending on the DAL (Design Assurance Level), a more or less accurate model of faults has to be defined. Identified faults and failures shall be mitigated or confined inside the Embedded Aircraft System using dedicated Hardware and/or Software mechanisms.

As detailed in part 9.4.2.3..4, Embedded Aircraft System integrity in multi-core platforms is closely linked to a correct transaction service in the interconnect. Here "correct" means that there is neither corruption nor any silent loss of transactions.

**Note:** The behavior of the interconnect between cores, memory and shared resources has to be known by design, by experimental test or by other means and present as a proof to reach acceptance of this component.

Even if cores and peripherals architecture have been inherited from an existing single-core processor, the current multi-core generation has introduced an important technological step mainly linked to the interconnect design.

**Note:** in most multi-core architectures, from Dual Core like in the P2020 (from Freescale), up to an octocore like in the P4080 (from Freescale) or a quad-core like in the ARM\_CORTEX®\_A15, the interconnect is the key point where all the accesses are performed. A chapter is dedicated to Interconnect Management.

Indeed, the interconnect has been built to sustain a higher bandwidth in order to serve efficiently all cores. They enable a high level of pipelining and parallelism in transaction services.

This growing complexity makes the set of all interconnect states highly difficult to determine and analyze - even with full information on the design (full information is not available even under dedicated NDA linked to manufacturer IP Policy).

<sup>&</sup>lt;sup>4</sup> NDA : Non Disclosure Agreement

<sup>&</sup>lt;sup>5</sup> IP : Intellectual Property

Thus, it may be difficult to obtain guarantees of correct transaction services in a general case. There are several approaches aimed at preventing inter-core conflicts with dedicated mechanisms, or limiting the interconnect load in order to remain in a "safe" mode. We plan to describe some approaches in the Interconnect Management Chapter.

#### 9.1.1.2. WCET analyzability

Worst Case Execution Time analyses aim at determining an upper bound for a piece of software's execution time. Usually, the result of a WCET analysis is an upper approximation of the exact WCET which is nearly impossible to determine for real life Software.

Simple architectures allow WCET determination using static analysis techniques using an execution model of the Airborne Embedded System. That means the analyzed software is not executed. Yet on complex COTS processors architectures, it is not possible to determine an accurate enough model. Today, an alternative method is used. A worst case scenario is defined from an analysis performed on the Airborne Software. The execution time is measured under this scenario, and is further corrected with parameters taking into account variable jitters and variability in the duration Airborne Embedded System operations.

When the Airborne Embedded System provider has no visibility into the deployed Airborne Software - for instance in an IMA -, **he shall determine and provide** such parameters to the Airborne Software suppliers and eventually to the Module Integrator.

The lack of information on the processor behavior may lead to pessimistic estimation of those parameters and degrade the approximation of the WCET.

For instance uncertainty on the cache content must lead to consideration of cache miss situations in the WCET analysis.

As detailed in part 9.4.2.3..5, the use of multi-core processors in Embedded Aircraft Systems worsens the WCET analyses. Indeed, the execution time of software on one core depends on software executed on the other cores because of potential inter-core conflicts. Moreover, it may be difficult to determine an upper bound on their impact whatever the concurrent software.

#### 9.1.1.3. Airborne Embedded System Usage Domain

When the Airborne Embedded System provider has little or no visibility into the deployed Airborne Software, he has to define what we call an "*Airborne Embedded System Usage Domain*" and provide it to the Airborne Software suppliers.

This Airborne Embedded System Usage Domain details usage limitations that shall be taken into account during Airborne Software development and execution.

Respecting the usage domain is a **mandatory and key** requirement. Dedicated tools may be used to automatically perform checks on the usage domain aspect. Moreover, protection mechanisms can be enforced to prevent usage domain violations that impact robust partitioning.

For instance, assembly instructions can be forbidden when their use impacts the integrity of the Airborne Embedded System. Various protection means can be highlighted:

- A privilege level restriction, which blocks the execution of the instruction

- A processor configuration that disables this instruction

- A mandatory integration test that checks the absence of such instructions

- A trusted piece of software that checks at runtime the absence of such instructions

Yet it shall be proven that in spite of such protections, no failure mode can lead to the execution of a forbidden instruction.

In the case of multi-Airborne Software systems, the Airborne Embedded Equipment usage domain is divided into two categories:

- Some restrictions deal with Airborne Software development and are destined for the Airborne Software Suppliers.

- Other limitations address the integration of Airborne Software and have to be handled by the Module Integrator.

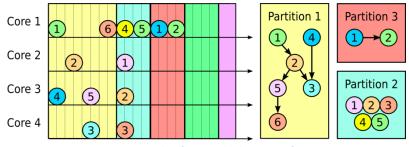

The use of multi-core processors is likely to entail changes in the Airborne Embedded System usage domains. Indeed, the presence of true parallelism between pieces of software (intra and/or inter-partitions in partitioned systems) adds new parameters that rule software deployment on the different cores.

We can illustrate examples of what could be these rules depending on the processor, the selected Operating System, the hypervisor (when required);

- Inside an Airborne Software installation, multiple critical sections cannot be accessed in parallel by different cores. Indeed, this situation might lead to deadlocks.

- Execution of processes inside a multi-core partition will be pre-allocated on the concerned cores (rather than dynamically allocated by the scheduler).

- In case determinism and/or robust partitioning cannot be absolutely demonstrated, it could be stated that a DAL-A partition is not allowed to be executed in parallel with other partitions

**Note:** In a low complex multi-core processor for example in a Dual-Core processor, this Usage Domain can be more easily demonstrated if Airborne Software is known and managed to match with safety requirements. When the Airborne Software is unknown, the Airborne Embedded Equipment usage Domain has to be defined as described above.

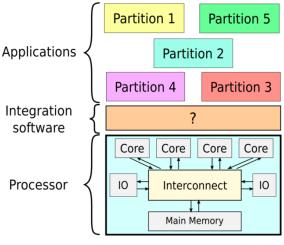

# 9.1.1.4. Robust Partitioning

Robust Partitioning is defined in various formulations in ARP4754, DO 297, ARINC 651 and ARINC 653. This is a property of fault containment. The reference study (Rushby, 1999) on robust partitioning was done by John Rushby for the FAA in 2000.

Robust partitioning is a mandatory requirement for partitioned Airborne Embedded Systems:

The reference definition for robust partitioning is named the *Gold Standard*:

"A partitioned system should provide fault containment equivalent to an idealized system in which each partition is allocated an independent processor and associated peripheral and all inter-partition communications are carried on dedicated lines"

Yet this general definition requires an accurate model of faults for Airborne Software. To the best of our knowledge, no direct proof of robust partitioning has been performed today. In practice, it is preferred the following stronger property, named the *Alternative Gold Standard* (introduced by David Hardin, Dave Greve and Matt Wilding):

"The behavior and performance of software in one partition must be unaffected by software in other partitions"

In IMA systems, an ARINC 653 Time and Space partitioning implementation ensures the Alternative Gold Standard.

Usually, robust partitioning is ensured through an analysis of interference channels. In multi-core systems, the possible presence of inter-core conflicts may introduce new channels. Two sub-problems occur:

- Is it possible to get rid of those channels?

- If no, will interference actually occur through those channels?

This problem is refined in part 9.4.2.3..6.

We have to notice that the property of **<u>Robust partitioning is not confined</u>** to IMA systems, as we have to deal with such requirements even in the first step of multi-core processor architectures like in a dual-core one or when Airborne Software applications of different DALs are executed by the different cores.

Robust partitioning can be ensured

- By a hardware mechanism if this mechanism exists in the processor, if it is described and accessible under dedicated privilege (Supervisor or Hypervisor mode),

- By the Operating System allocating priority to the Airborne Software with the highest level of DAL (DAL-A for example) when Airborne Software of different DAL levels is executed in the Airborne Embedded System.

- Or directly by the Airborne Software at Airborne Embedded System level. At this level, it can be done <u>only</u> if we can master the temporal execution of each Airborne Software application and solve the conflicts at this level (threads of processes allocation and description).

# 9.1.2. Certification objectives for Embedded Aircraft Systems

When taking into account the general certification requirements, the Airborne Embedded System provider must address the following objectives:

- Ensure Intended Function,

- Meet Safety Objectives,

- Sustain Foreseeable Conditions.

Note that this chapter does not replace applicable requirements such as S/HW compliance with XX.1301/XX.1309, i.e. development assurance as defined by ED-12B/DO-178B and ED-80/DO-254.

This chapter and this report focus on multi-core processor where ED-12B/DO-178B for embedded micro-code and/or ED-80/DO-254 for processor Hardware development are not used by processor manufacturer.

At equipment level and/or board level, Airborne Embedded System providers and/or Airborne Software providers have to be compliant with ED-80/DO-254 and ED-12/DO-178 (B or C) and implement mitigation to demonstrate the global compliance with ED-80/DO-254 and/or DO-178 with such components as processors.

# 9.1.2.1. Intended Function

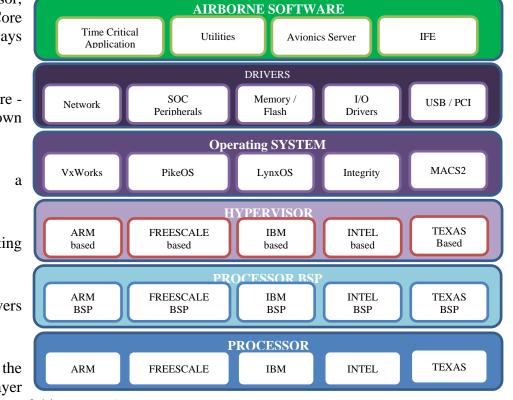

The functionalities of a processor, whether it is COTS Mono-Core or Multi-Core, are always exercised using:

- First a layer of Hardware -Software interface known as the processor BSP<sup>6</sup>,

- When required, a Hypervisor layer

- Then the Operating System itself,

- All the required drivers and Processor drivers

- And the last one the ARM Airborne Software layer (which is out of the scope of this purpose).

<sup>&</sup>lt;sup>6</sup> BSP : Board Support Package

# 9.1.2.1..1 BSP or Board Support Package

A software layer that adapts the Operating System to the dedicated processors. This layer gives accesses to the internal resources of the multi-core component but the management of these resources has to be done by the Hypervisor when required or by the Operating System.

BSP development has to fulfill ED-12/DO-178 (B or C) requirements.

**BSP\_Remark1**: When a Hypervisor is not required, privileged access has to be given in Supervisor or Hypervisor mode to the Operating System to allow programming of shared resources like hardware accelerators, arbiters, in order to fulfill safety requirements such as determinism.

**BSP\_Remark2:** if two Operating Systems are used, for example, on a dual-core processor, one of these two Operating Systems has to be set in the Supervisor or Hypervisor mode to have the privilege to access to programming of shared resources, the second one has to be set respectively in User or Supervisor mode.

#### 9.1.2.1..2 **Hypervisor**

A software layer that acts as a Virtual Machine Monitor. This software layer emulates virtual environments in which several Operating Systems may be executed simultaneously. In such a configuration, its use may help mastering the processor behavior regarding dedicated requirements like determinism or conflict management in shared resources accesses.

We consider, in this report that the Hypervisor level is realize in a SMP mode managing all cores.

# RGL n°1

When an Hypervisor is required to manage the behavior of the interconnect, the development of such a Hypervisor **shall fulfill** ED-12/DO-178 (B or C) requirements at the corresponding Design Assurance Level, at least the most stringent Airborne Software.

**HYP\_Remark1**: we see that there is a relationship between the intended function and objectives with respect to safety and foreseeable conditions, as, at least for functional operation, the influence of external Airborne Software input authority is limited by such a hypervisor, while the latter is providing the deterministic behavior, performance characteristics and integrity necessary to the end-user Airborne Software.

The use of a Hypervisor layer **is not mandatory**, for example in a dual core processor, where the behavior of this dual-core processor can be managed directly at the Airborne Software level.

Let us detail this:

• We are able to master the complete behavior of Airborne Software application(s) running on the processor even in SMP mode (during any one period of time, the multi-core processor is allocated

to only one Airborne Software application running and the Operating System realizes the tasks or processes allocations on cores) or in AMP mode (during one period of time, each core runs a dedicated Airborne Software application, which means that we have one Operating System per core),

We can demonstrate that there are no shared resource access conflicts by analyzing the execution of the Airborne Software and/or processes or threads. Or if there are conflicts, they are managed by arbitration using priorities based on the DAL level of the Airborne Software: if two DAL-A Airborne Software applications have to be executed at the same time, prioritization is not the solution → the only solution remains the hypervisor that manages the Interconnect Usage Domain and provides safe arbitration between the Airborne Software applications.

**HYP\_Remark2**: if a Hypervisor is not required, the Airborne Software applications have to be clearly described to demonstrate the absence of conflicts (between Airborne Software in AMP or between threads or processes in SMP) or that conflicts are managed using, for example, Airborne Software DAL level for managing access priorities to shared resources.

# 9.1.2.1..3 **Operating System**

Software that manages computer Hardware resources and provides common services for Airborne Software. The operating system is a vital component of the system software in a computer system. Airborne Software programs require an operating system to function.

We can notice various types of Operating System such as:

- Real-time

- A multitasking operating system that aims at executing real-time Airborne Software. Realtime operating systems often use specialized scheduling algorithms so that they can achieve a deterministic nature of behavior. The main objective of real-time operating systems is their quick and predictable response to events. They have an event-driven or time-sharing design that switches between tasks based on their priorities or external events while time-sharing operating systems switch tasks based on clock interrupts.

- Multi-user

- A multi-user operating system allows multiple users to access a computer system at the same time. Note that Single-user operating systems have only one user but may allow multiple programs to run at the same time.

- Multi-tasking vs. single-tasking

- A multi-tasking operating system allows more than one program to be running at a time; an ARINC653 Operating System is a Multi-tasking one. A single-tasking system has only one running program. Multi-tasking can be of two types: pre-emptive or co-operative. In preemptive multitasking, the operating system slices the CPU time and dedicates one slot to each of the programs.

- Distributed

- A distributed operating system manages a group of independent cores and makes them appear to be a single processor..

- Embedded

- They are designed to operate on small machines like PDA<sup>7</sup>'s with less autonomy. They are able to operate with a limited number of resources. They are very compact and extremely efficient by design.

The development of an Operating System has to fulfill ED-12/DO-178 (B or C) requirements and when required, for IMA for example, ARINC653 requirements as well.

# 9.1.2.1..4 **Device drivers**

Pieces of software developed to mask the complexity of interactions with Hardware devices. The device driver constitutes an interface for communicating with the device, through the specific computer bus or communications subsystem that the hardware is connected to. A device driver is a specialized hardware-dependent computer program which is also operating system specific that enables another program, typically an operating system or Airborne Software package or computer program running under the operating system kernel, to interact transparently with a hardware device, and usually provides the requisite interrupt handling necessary for any necessary asynchronous time-dependent hardware interfacing needs.

The development of Device drivers has to fulfill ED-12/DO-178 (B or C) requirements

#### 9.1.2.2. Safety Objectives